RISC-V 5 Stage Pipelined Processor

RISC-V 5 Stage Pipelined Processor

Description:

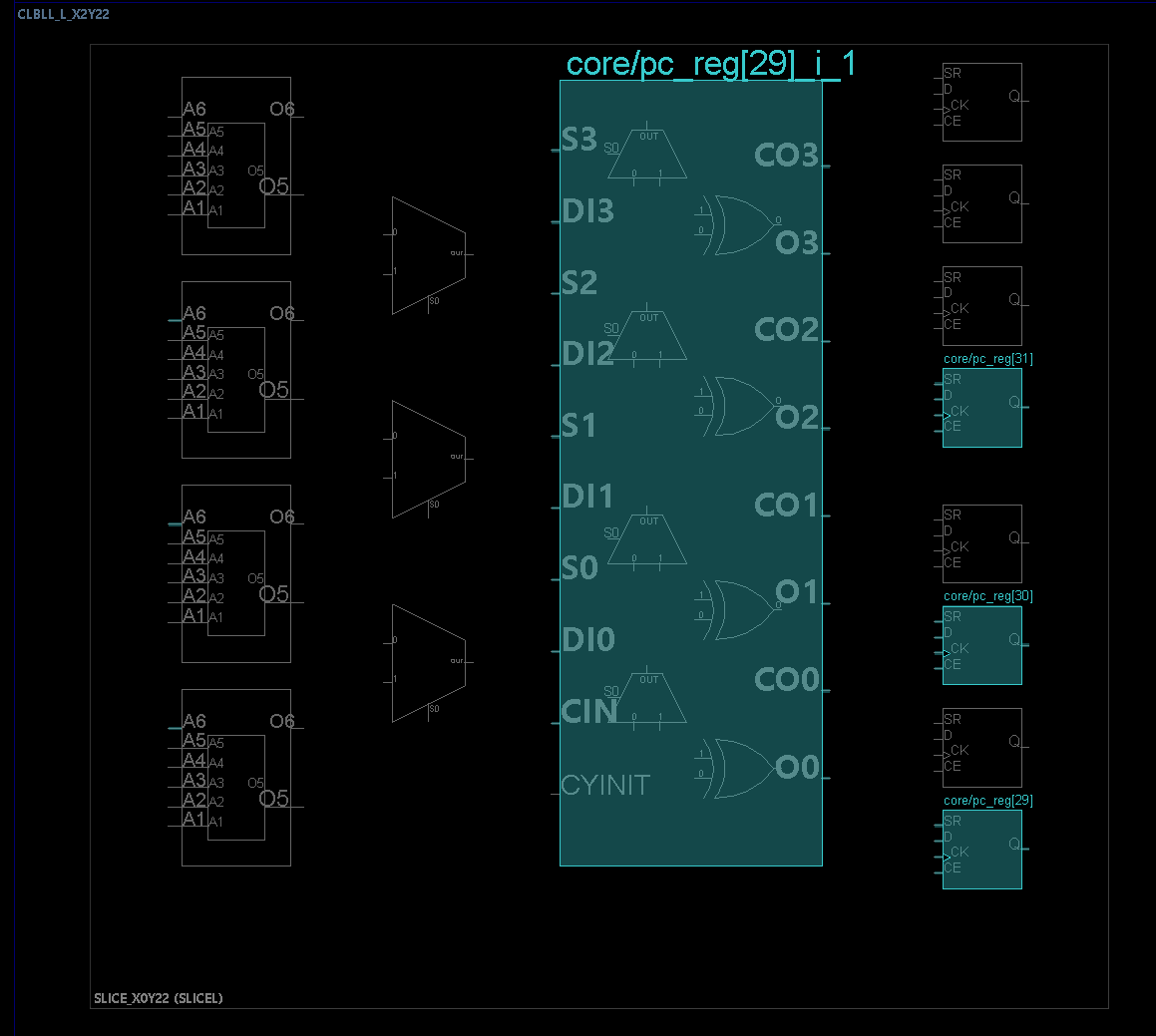

This project involved the design and implementation of a fully-functional 5-stage pipelined RISC-V processor using SystemVerilog, featuring a complete instruction set architecture supporting R-Type, I-Type, S-Type, B-Type, J-Type, and U-Type instructions. The processor implements a classic Harvard architecture with separate instruction and data memories, and incorporates sophisticated hazard detection and forwarding mechanisms to handle both data and control hazards efficiently. The design includes all essential components: program counter logic, register file, arithmetic logic unit (ALU), control unit, immediate generator, branch prediction unit, and pipeline registers between each stage (IF, ID, EX, MEM, WB). A comprehensive testbench was developed with automated verification, coverage analysis, and multiple test programs to validate instruction execution, memory operations, branching behavior, and hazard handling scenarios, ensuring robust performance and correct operation under various conditions.