FPGA Sorting Hardware Accelerator

FPGA Sorting Hardware Accelerator

Description:

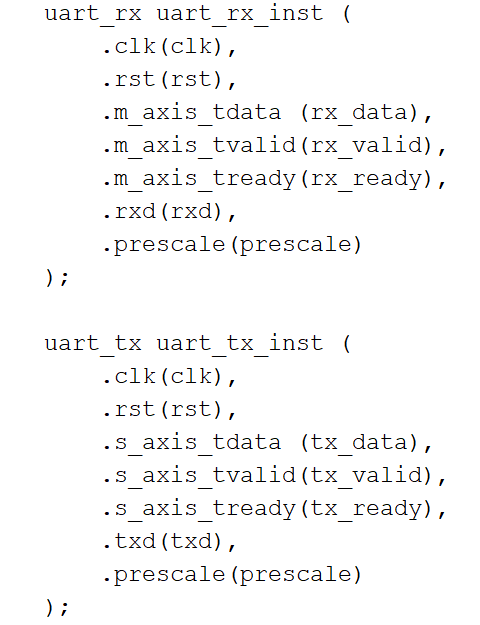

I designed and validated a complete end-to-end radix sorting system on the iCE40 FPGA, integrating hardware architecture, control logic, and verification into a single deployable design. The system accepts unsorted data over UART using a robust ready/valid handshake, buffers transactions through a read-priority synchronous FIFO, and performs high-throughput counting sort using 1024 block-RAM buckets. I optimized the design to close timing at 12 MHz with only ~16% LUT utilization, while resolving subtle RAM read-after-write hazards and FIFO push/pop race conditions to ensure deterministic correctness. Functional accuracy and performance were verified using a comprehensive SystemVerilog testbench and Python hardware harnesses that measured round-trip latency and sustained burst throughput. The finalized build flow (sv2v → yosys → nextpnr → icepack) produces a reproducible, ready-to-flash bitstream with automated testing support.