FPGA Seven Segment Display Driver

FPGA Seven Segment Display Driver

Description:

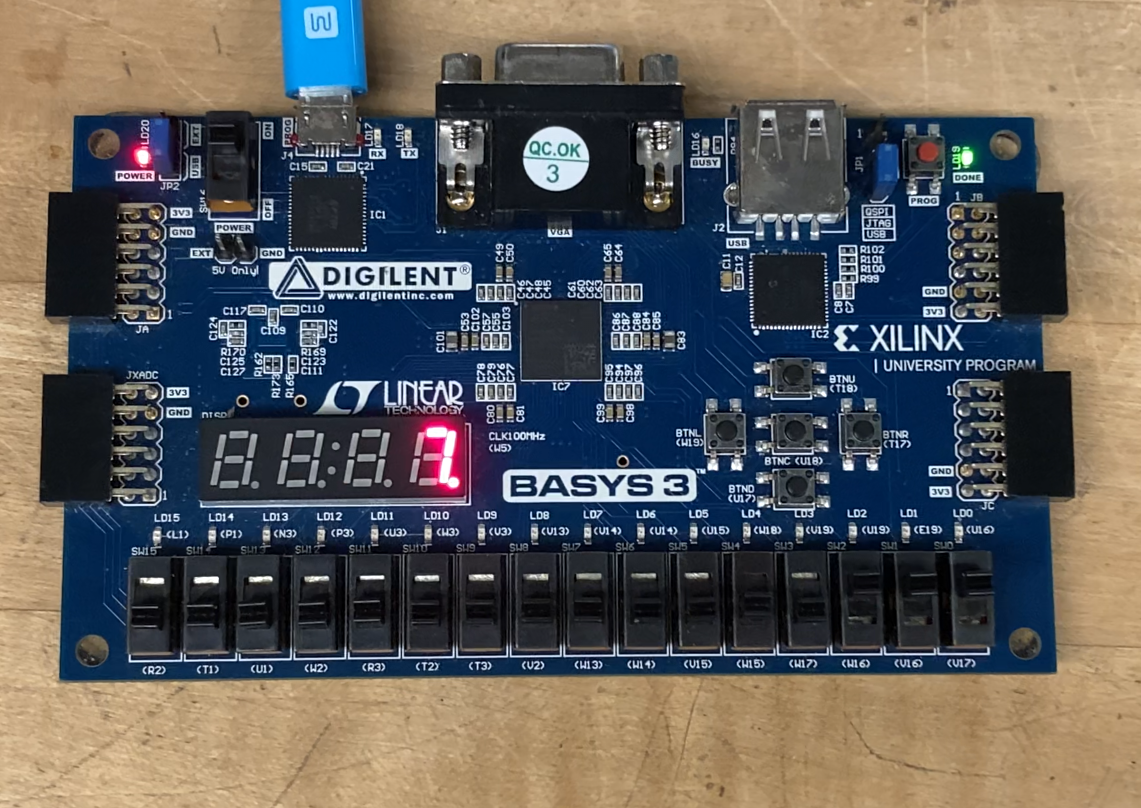

This assignment challenges you to design and implement a combinational logic module in Verilog that translates a 3-bit octal input (from switches d2–d0) and a pushbutton input (for the decimal point) into the corresponding signals for a single digit on the Basys 3 7-segment display. You will derive and encode the Boolean equations for each segment (CA–CG) using only bitwise operators (&, |, ~, ^) within assign statements, and you’ll configure the digit enable lines (AN0–AN3) to activate only the rightmost display. As part of the workflow, you’ll modify the Basys 3 constraints file to map your module’s ports to the appropriate FPGA pins, synthesize and implement the design in Vivado to generate a bitfile, and then download and demonstrate the functionality on the physical board. This lab reinforces mastery of combinational logic design, Verilog syntax constraints, and FPGA toolchain practices essential for embedded digital systems.