FPGA DVS Gesture Classifier

FPGA DVS Gesture Classifier

Description:

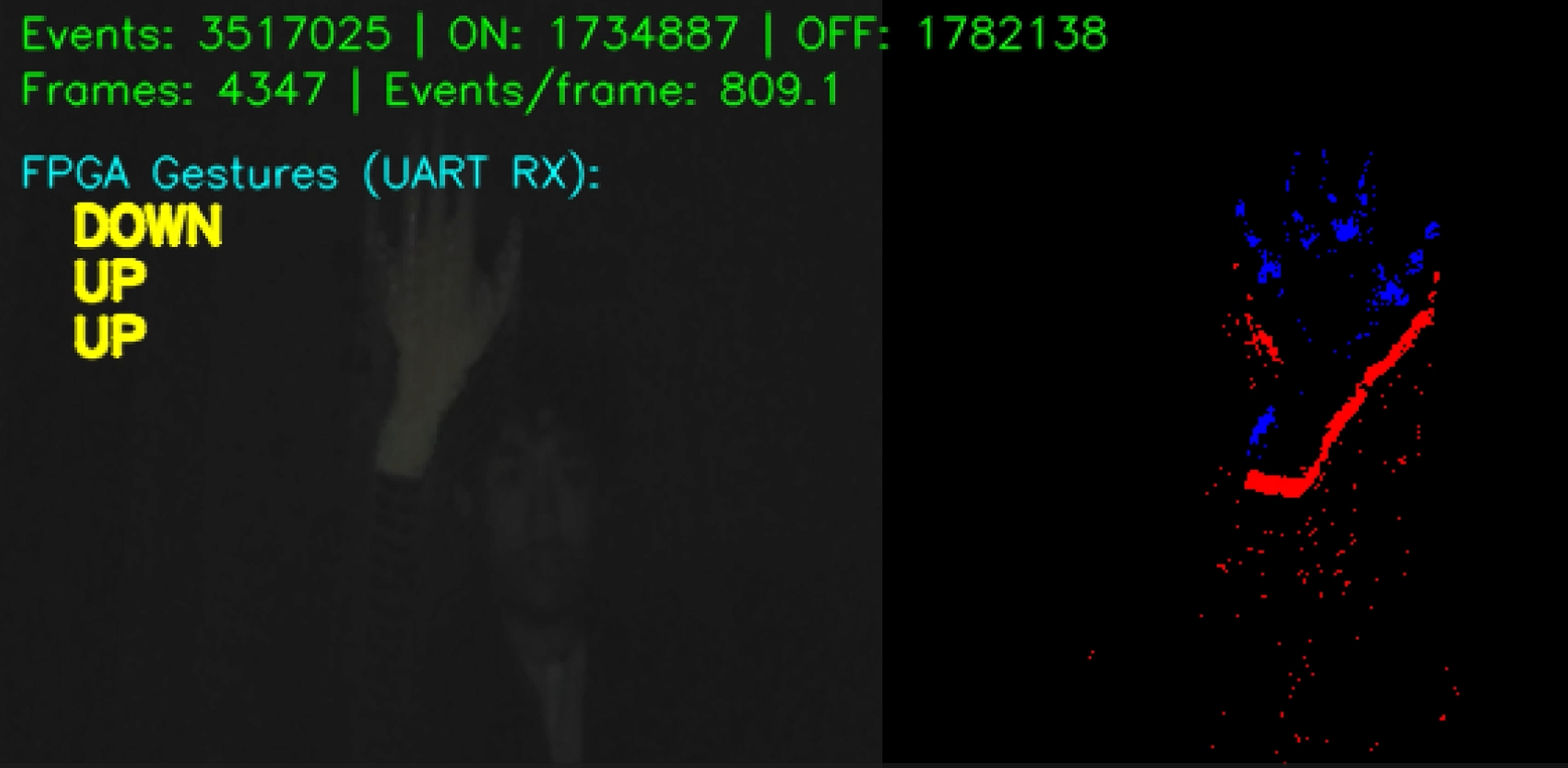

FPGA-DVS-Gesture-Classifier is a real-time embedded vision project that runs gesture recognition directly on a Lattice iCE40UP5K FPGA using event data from a Prophesee GenX320 dynamic vision sensor. The system streams EVT2.0 camera events over UART into an FPGA pipeline that decodes the asynchronous pixel events, compresses the 320×320 sensor output into an 8×8 spatial grid, accumulates activity across four temporal bins, and flattens the result into a 256-feature vector for classification. It then uses a tiled systolic-array-based matrix-vector engine to score four gesture classes—Down, Left, Right, and Up—and applies argmax plus persistence logic so only stable predictions are reported back over UART and displayed on LEDs. The project also includes a full verification and deployment flow with cocotb testbenches, synthesis through the open-source iCE40 toolchain, and flashing support, making it a strong demonstration of FPGA design, event-based vision processing, and hardware-efficient machine learning inference.