Finite State Machine Quick Add Game

Finite State Machine Quick Add Game

Assignment Purpose:

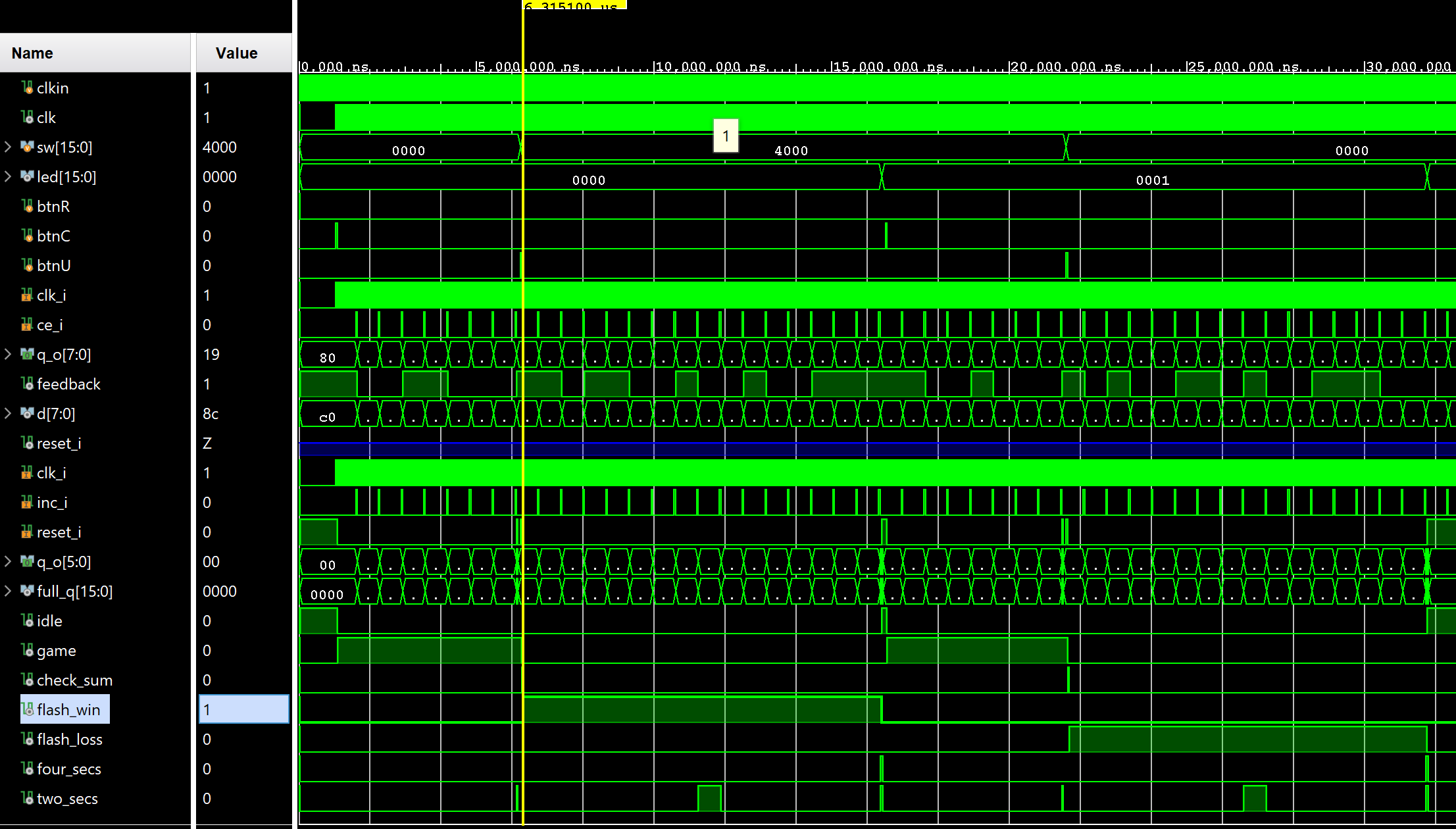

In this lab, you will design and implement a fully synchronous digital system in Verilog that functions as an interactive “Quick Add” training game on the BASYS3 FPGA board. The core of the project is a one-hot–encoded finite state machine (FSM) that orchestrates game rounds by generating and displaying three random numbers (two 3-bit operands and one 4-bit target), timing each round with a loadable down counter, and comparing the sum of the operands against the target. A linear feedback shift register (LFSR) provides pseudo-random inputs, while 7-segment displays and LEDs visualize the game state: showing new random values every two seconds, detecting a “stop” button press, flashing displays to indicate a correct or incorrect match, and updating a 16-bit LED shift register to track successes or failures. Throughout, all combinational logic is restricted to bitwise operators ( &, |, ˜, ˆ ) and ‘assign’ statements, and all sequential elements use positive-edge flip-flops clocked by a single system clock. This assignment reinforces synchronous FSM design, clock-enable usage for timed events, LFSR implementation for randomness, and top-level integration of multiple modules in a real-world FPGA environment.