Behavioral Verilog

Behavioral Verilog

Description:

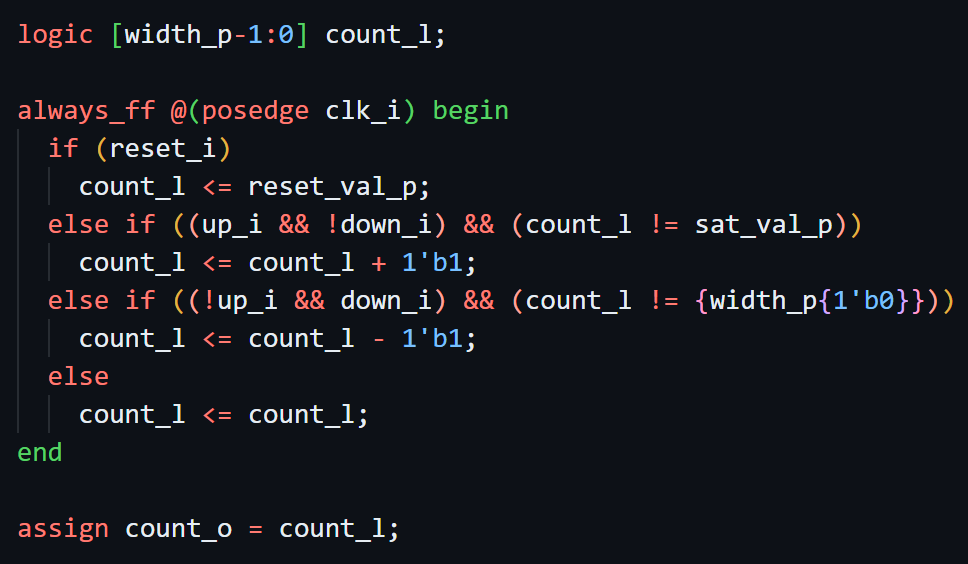

To complete this lab, I implemented a variety of digital logic modules using behavioral SystemVerilog, focusing on both combinational and sequential design principles. I began by writing combinational modules such as XOR, XNOR, multiplexers, adders, and binary/Gray code converters using always_comb and assign statements, then verified correctness through simulation and waveform analysis. I also created a seven-segment display decoder (hex2ssd) and tested it on the FPGA by integrating it with my design from Lab 1. In the sequential section, I implemented parameterized counters, shift registers, debouncing logic, and edge detection circuits using always_ff, connecting them to physical buttons on the FPGA to demonstrate controlled counting behavior on the display. Finally, I designed and simulated Moore and Mealy state machines—one detecting the Konami code sequence and another recognizing directional joystick patterns—to reinforce my understanding of finite-state design and input synchronization. Through coding, simulation, and FPGA testing, I gained hands-on experience in hardware modeling, timing control, and real-time digital logic verification.