16 Bit Loadable Counter

16 Bit Loadable Counter

Purpose of the Assignment:

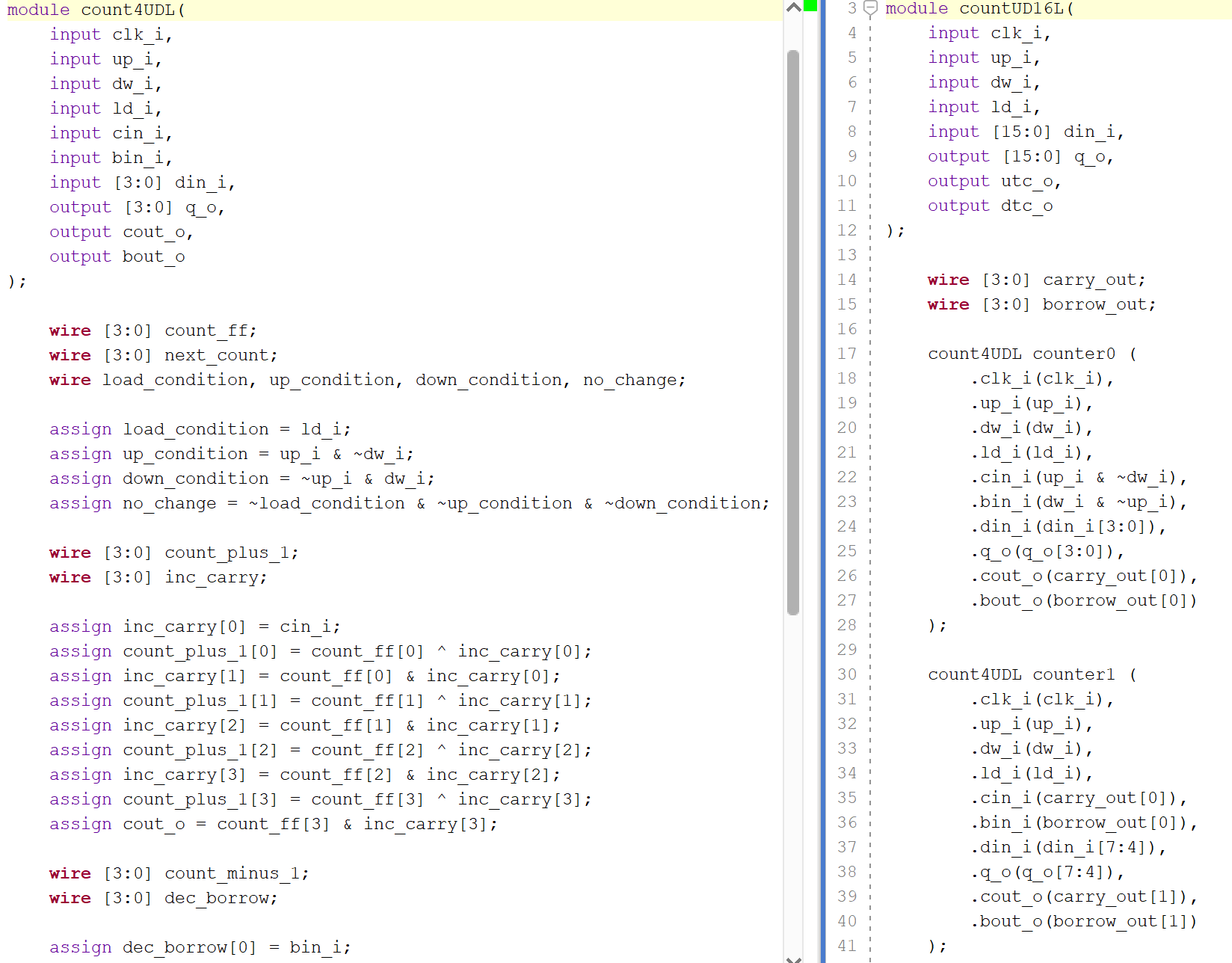

In this lab, you will design and implement a fully synchronous 16-bit counter in Verilog that supports up/down counting, parallel loading, and continuous counting modes, and then drive it to four hexadecimal 7-segment displays. To accomplish this, you’ll start by building a 4-bit loadable counter using only positive-edge flip-flops (FDRE) and bitwise operators, verify its terminal-count outputs (UTC/DTC), and then cascade four instances to form a 16-bit counter. Alongside, you’ll create an edge detector to capture pushbutton presses for single-step increments/decrements, a ring counter to multiplex the four display digits, and a 4-to-1 selector to feed each 4-bit nibble to a single hex-to-7-segment decoder. Pushbuttons will control increment, decrement, continuous count (with wrap-around at FFFC–FFFF), and parallel load from a 16-bit switch bus. LEDs will indicate when the counter has reached 0 or FFFF. This assignment reinforces fundamental concepts of synchronous digital design—clock-edge triggering, modular hierarchy, and resource-efficient combinational logic—while integrating multiple submodules into a cohesive, on-FPGA demonstration that displays a 16-bit value in hexadecimal.